FCO7LPG可編程差分振蕩器多少錢

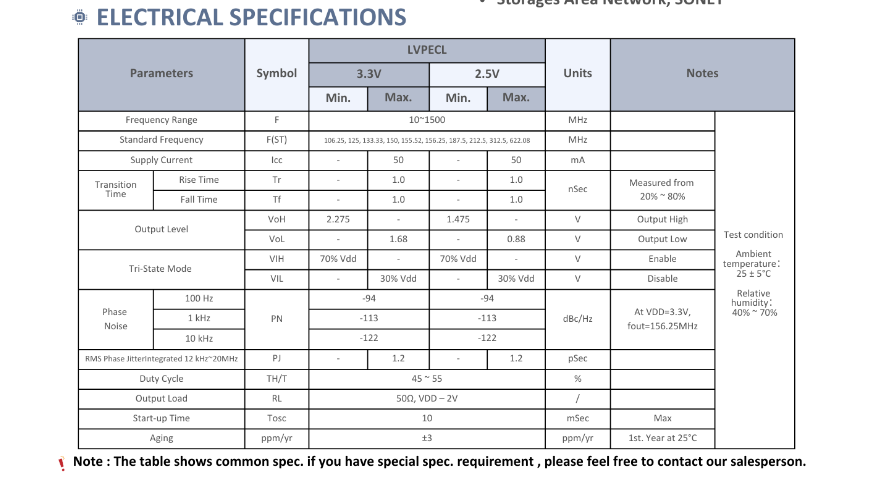

雷達信號處理平臺中的時鐘一致性保障 現代雷達系統對目標探測、回波捕捉與波束處理提出了極高的實時性和精度要求。雷達內部的信號鏈路包括射頻接收、模數轉換、DSP預處理、波束合成與目標識別等環節,每一步都高度依賴于一個低抖動、高穩定的時鐘信號。在這種背景下,FCom富士晶振推出的可編程差分振蕩器成為雷達信號處理平臺中不可或缺的關鍵組件。 FCom產品支持10MHz~250MHz全覆蓋頻率段,常用頻點如50MHz、100MHz、125MHz、156.25MHz等可通過OTP或I2C方式靈活配置,極大適配雷達多通道信號處理平臺。輸出接口支持LVDS、HCSL、LVPECL,可針對不同前端板卡選擇佳兼容方式,有效減少串擾與信號損失。其低至0.05ps RMS的相位抖動特性突出提升了雷達系統的探測靈敏度和分辨率。通過固件升級,可編程差分振蕩器支持頻率重新配置。FCO7LPG可編程差分振蕩器多少錢

可編程差分振蕩器

該振蕩器的頻率穩定度控制在±10ppm以內,在極端溫度環境下(-55~+125℃)仍可保持時鐘精確輸出。封裝方面,FCom提供7050、5032等多規格工業級氣密封封裝,滿足雷達系統對抗震、抗干擾、防潮的使用需求。特別適用于相控陣雷達、海事雷達、機場航跡管理系統與前沿氣象探測設備等場景。 此外,FCom產品支持雙頻冗余備份與軟切換機制,在主通道失效時自動調用備用時鐘路徑,進一步增強了雷達信號鏈的系統穩定性。通過GUI配置工具,工程人員可快速在開發階段切換頻點、修改接口邏輯,從而降低設計風險與調試成本。定制可編程差分振蕩器系列項目驗證期推薦使用可編程差分振蕩器快速迭代調頻。

數據加速接口系統中的高速時鐘支撐 在AI服務器、智能邊緣平臺與高性能存儲系統中,數據加速接口如PCIe Gen4/Gen5、CXL 2.0/3.0、NVLink等被各個方面應用。這些高速互聯接口對時鐘信號的要求極為嚴苛,必須具備極低抖動、低延遲啟動與多接口兼容能力。FCom富士晶振的可編程差分振蕩器正是為這一類高速數據接口而量身定制。 該系列振蕩器支持25MHz、100MHz、125MHz、156.25MHz、200MHz、250MHz等主流頻點,輸出接口支持LVDS、HCSL、PECL,可直接驅動多種SerDes鏈路控制器、交換芯片、PCIe Retimer模塊和CXL Host Bridge。

量子計算控制平臺的超高穩定時鐘參考 量子計算平臺的控制系統通常包含精密的激勵脈沖生成器、量子位讀出電路、鎖相環管理、超導器件驅動與同步ADC/DAC模塊,其性能高度依賴低噪聲、高穩定、可定制的時鐘系統。FCom富士晶振可編程差分振蕩器通過數字調控機制與極限低抖動特性,在量子計算控制系統中提供高一致性、低失調的時鐘基準。 該系列支持10MHz~250MHz頻率自定義,輸出接口為LVPECL或LVDS,滿足主控FPGA、射頻控制器、高速模數轉換鏈路的同步與觸發要求。其0.05ps RMS抖動性能可大限度降低量子比特激勵干擾,提高相干時間與讀出準確率。 產品支持OTP頻率寫入、主控動態頻率設置與片上冗余輸出切換,適合多通道并行操作的實驗級平臺部署。 其高可靠封裝設計通過靜電保護與熱漂抑制測試,在實驗室冷卻腔體、高溫合成器與電磁屏蔽倉環境下均可穩定工作。目前該器件已在國內多家量子實驗室與商業量子計算平臺中完成關鍵試驗驗證。前沿視頻平臺采用可編程差分振蕩器優化幀同步。

智能交通控制系統中的時鐘標準化建設 智能交通控制系統集成車路協同、信號燈管理、視頻識別、邊緣計算等多種功能,對設備間的時鐘同步與模塊間的數據一致性提出了嚴格要求。尤其是在多源圖像融合、車道識別、紅綠燈自適應調度等環節,要求系統中每個子模塊都具備高穩定性、低延遲、精確同步的時鐘輸入。FCom富士晶振推出的可編程差分振蕩器正適用于構建統一時鐘管理平臺,為智能交通系統提供強力支撐。 產品支持24MHz、27MHz、74.25MHz、100MHz、125MHz等頻率配置,輸出格式為LVDS/HCSL/CMOS,能夠驅動信號控制器、AI攝像模塊、交通協調通信模塊與圖像融合主控板等關鍵設備。可編程特性支持單顆振蕩器輸出多頻點并統一啟停管理,實現交通節點控制設備的時鐘標準化部署。 在抗干擾方面,FCom產品通過多項電磁兼容性測試,在路側設備高壓閃斷、無線電干擾與雷擊浪涌環境下仍保持輸出穩定,頻率穩定度達±10ppm,極大保障交通信號的調度連續性。 產品封裝適配車規級與工業級應用標準,適合于交通路口控制箱、高速ETC系統、智慧路側站、信號協調中心等環境惡劣但時序要求嚴格的部署點。可編程差分振蕩器有助于構建統一的時鐘管理系統。國產可編程差分振蕩器一般多少錢

衛星通信終端中各個方面采用可編程差分振蕩器輸出基頻。FCO7LPG可編程差分振蕩器多少錢

數據中心服務器主板中的可編程差分時鐘應用 現代數據中心服務器主板集成多通道處理器、DDR4/DDR5內存、PCIe Gen4/Gen5高速擴展、網絡控制器與NVMe存儲模塊,對系統時鐘提出高頻、高一致性、低抖動的嚴格要求。特別是主板多接口協同運行時,對差分時鐘信號之間的偏移、串擾與Jitter Budget控制容忍度極低。FCom富士晶振的可編程差分振蕩器,正是在這種高性能平臺中提供關鍵時鐘支撐的理想選擇。 在服務器主板上,FCom可編程差分振蕩器通常用于以下關鍵位置: - 作為CPU或北橋芯片參考時鐘 - PCIe總線控制器時鐘源(如100MHz HCSL) - 網絡PHY芯片參考頻率(如156.25MHz LVDS) - DDR控制器或高速ADC同步輸入 - NVMe集線器或鏈路復位控制端FCO7LPG可編程差分振蕩器多少錢

- 壓控振蕩器VCXO廠家供應 2025-07-25

- FC5LPG可編程差分振蕩器工廠直銷 2025-07-24

- 有什么可編程差分振蕩器常用知識 2025-07-24

- 車規級VCXO單價 2025-07-24

- 可編程差分振蕩器制造價格 2025-07-24

- 壓控晶體振蕩器VCXO客服電話 2025-07-24

- 高精度VCXO客服電話 2025-07-24

- FVC3XVCXO客服電話 2025-07-24

- FVC-5XVCXO批量定制 2025-07-24

- 本地可編程差分振蕩器技術指導 2025-07-24

- 鎮江顯影機服務價格 2025-07-25

- 浙江穩定PT鉑電阻 2025-07-25

- 安徽巨型二極管哪家好 2025-07-25

- 宜興制造SMT貼片加工廠家現貨 2025-07-25

- 杭州電木ksd301 2025-07-25

- 使用開合機械屏廠家報價 2025-07-25

- 北京JC15連接器價格 2025-07-25

- 寧波插件保險絲哪家好 2025-07-25

- LED驅動觸控開關芯片研發 2025-07-25

- 南京質量Pcba加工哪家好 2025-07-25