汕頭RFFE協(xié)議分析儀那家好

如果在時(shí)鐘沿檢測(cè)器重置之前出現(xiàn)第二個(gè)時(shí)鐘沿(在個(gè)時(shí)鐘沿后),為避免數(shù)據(jù)丟失需要兩個(gè)樣本。在跳變定時(shí)中,每個(gè)序列步驟只有2個(gè)分支。在跳變時(shí)序中,只有一個(gè)全局計(jì)數(shù)器可用。跳變時(shí)序需要有時(shí)間標(biāo)簽才能重建數(shù)據(jù)。通過將時(shí)間標(biāo)簽與內(nèi)存中的測(cè)量數(shù)據(jù)交叉可存儲(chǔ)時(shí)間標(biāo)簽。默認(rèn)情況下,分析儀將查找為邏輯分析儀模塊定義的所有總線/信號(hào)上的轉(zhuǎn)變。但是,為增加可用內(nèi)存深度和采集時(shí)間,可以在高級(jí)觸發(fā)中選擇不存儲(chǔ)某些總線/信號(hào)轉(zhuǎn)變(如將無用信息添加到測(cè)量中的時(shí)鐘或選沖信號(hào))。運(yùn)行測(cè)量時(shí),無論總線/信號(hào)是否定義或是否分配給邏輯分析儀通道,都將在所有這些通道上采集數(shù)據(jù)。在跳變時(shí)序模式中,如果定義的總線/信號(hào)(未排除的)上存在轉(zhuǎn)變,將保存采集的樣本。運(yùn)行跳變時(shí)序測(cè)量后,如果為以前未分配的邏輯分析儀通道定義新的總線/信號(hào),那么將顯示在這些通道上采集的數(shù)據(jù),但是不可能存儲(chǔ)這些總線/信號(hào)上的所有轉(zhuǎn)變;顯示的數(shù)據(jù)好似新的總線/信號(hào)在運(yùn)行測(cè)量前就已經(jīng)被排除了。在跳變時(shí)序中,不需要預(yù)先存儲(chǔ)數(shù)據(jù)(觸發(fā)前獲得的樣本)。因此,與狀態(tài)模式非常相似的是,觸發(fā)位置(起始/中心/結(jié)束)表明觸發(fā)后樣本占用內(nèi)存的百分比。JTAG協(xié)議分析儀/訓(xùn)練器找歐奧!汕頭RFFE協(xié)議分析儀那家好

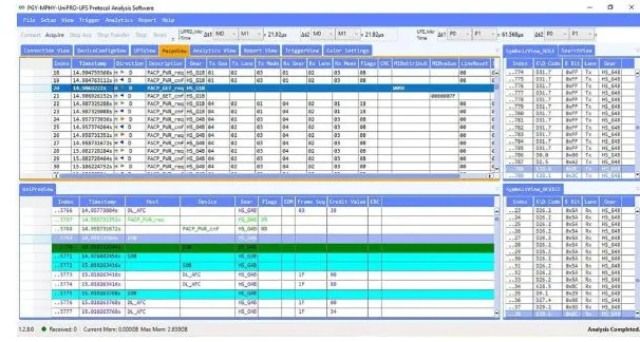

序列步驟存儲(chǔ)總會(huì)覆蓋默認(rèn)存儲(chǔ),但只針對(duì)序列步驟存儲(chǔ)中特別指定的條件。處理默認(rèn)存儲(chǔ)和序列步驟存儲(chǔ)之間的時(shí)一定要謹(jǐn)慎。雖然設(shè)置邏輯分析儀很困難,但觸發(fā)函數(shù)可以降低此過程的難度。觸發(fā)函數(shù)是可以組合起來設(shè)置觸發(fā)的常用構(gòu)建塊。由于這些函數(shù)涵蓋了多數(shù)普通觸發(fā),因此通過選擇適當(dāng)?shù)暮瘮?shù)并將其填充到數(shù)據(jù)中即可設(shè)置觸發(fā)。下圖顯示了邏輯分析儀觸發(fā)用戶界面。請(qǐng)注意,觸發(fā)函數(shù)位于屏幕左側(cè)的一個(gè)醒目位置。圖21使用觸發(fā)函數(shù)通常,設(shè)置復(fù)雜觸發(fā)的難題是對(duì)問題進(jìn)行分解。換句話說,就是如何將復(fù)雜觸發(fā)映射到序列步驟、分支和布爾邏輯表達(dá)式。將問題分解為不同時(shí)發(fā)生的事件。這些事件對(duì)應(yīng)于序列步驟。掃描觸發(fā)函數(shù)列表,嘗試找出一些與步驟1中確定的事件相匹配的函數(shù)。將所有剩余事件分解為布爾邏輯表達(dá)式及其相應(yīng)操作。各個(gè)布爾邏輯表達(dá)式/操作對(duì)分別對(duì)應(yīng)于序列步驟中的一個(gè)單獨(dú)分支。請(qǐng)記住,可能存在只用于為序列步驟處理存儲(chǔ)限定的“存儲(chǔ)”分支。設(shè)置邏輯分析儀觸發(fā)與編寫軟件相徑庭。如果使用預(yù)定義的觸發(fā)函數(shù)和較早編寫的文檔完善的觸發(fā)來完成其他工作,就可降低設(shè)置邏輯分析儀觸發(fā)的難度。在沒有其他可用的資源時(shí),才需要編寫自己的觸發(fā)設(shè)置。后。東莞I2C/SPI協(xié)議分析儀找哪家SDIO協(xié)議分析儀/訓(xùn)練器找歐奧!

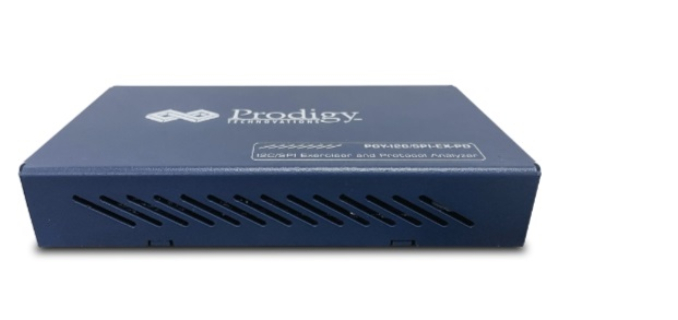

但由于“轉(zhuǎn)到”操作,剩余的序列步驟可以以任意順序執(zhí)行。執(zhí)行一個(gè)序列步驟且布爾邏輯表達(dá)式均為假時(shí),邏輯分析儀將采集下一樣本并再次執(zhí)行同一序列步驟于“KeepacquiringmoresamplesuntilDATA=7000,thentrigger”。如果符合一個(gè)序列步驟中的布爾邏輯表達(dá)式,那么在執(zhí)行下一序列步驟之前總是采集另一樣本。換句話說,如果一個(gè)樣本符合序列步驟1的條件,在執(zhí)行序列步驟2前將采集另一樣本。這意味著一個(gè)單獨(dú)的樣本不可能符合多個(gè)序列步驟的條中的條件二者之間采集了新的樣本,因此邏輯分析儀不會(huì)在采集樣本#1時(shí)觸發(fā)。可將此觸發(fā)序列看作是“FindADDR=1000followedbyDATA=2000andthentrigger”。觸發(fā)序列中的多序列步驟暗示了“后接”。邏輯分析儀觸發(fā)后,將不會(huì)再次觸發(fā)。換句話說。歐奧電子是Prodigy在中國(guó)區(qū)的官方授權(quán)合作伙伴,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測(cè)試解決方案不會(huì)收到EAR進(jìn)出口方面的管制。同時(shí)還有代理其他總類的協(xié)議分析儀,包括嵌入式設(shè)備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓(xùn)練器,I3C協(xié)議分析儀及訓(xùn)練器,RFFE協(xié)議分析儀及訓(xùn)練器等等。我司還有代理SPMI協(xié)議分析儀及訓(xùn)練器,車載以太網(wǎng)分析儀,以及各種相關(guān)的基于示波器的解碼軟件和SI測(cè)試軟件。

歐奧電子是Prodigy在中國(guó)區(qū)的官方授權(quán)合作伙伴,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測(cè)試解決方案不會(huì)收到EAR進(jìn)出口方面的管制。同時(shí)還有代理其他總類的協(xié)議分析儀,包括嵌入式設(shè)備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓(xùn)練器,I3C協(xié)議分析儀及訓(xùn)練器,RFFE協(xié)議分析儀及訓(xùn)練器等等。我司還有代理SPMI協(xié)議分析儀及訓(xùn)練器,車載以太網(wǎng)分析儀,以及各種相關(guān)的基于示波器的解碼軟件和SI測(cè)試軟件。同時(shí),歐奧電子也有提供高難度焊接,以及高速信號(hào),如UFS,DDR3/DDR4,USBtypeC等高速協(xié)議抓取和分析的服務(wù)。對(duì)于分析高速并行總線就不能勝任了。更進(jìn)一步的設(shè)計(jì),需要增加FPGA、SRAM等器件,才能解決速度不夠和通道數(shù)量不足的問題。圖2圖3圖4下面就以Saleae邏輯分析儀為例,通過采樣分析I2C總線波形和PWM波形,簡(jiǎn)單介紹它的特點(diǎn)和使用方法。先介紹用邏輯分析儀采樣單片機(jī)對(duì)I2C器件AT24C16的寫數(shù)據(jù)過程。硬件連接先將邏輯分析儀的GND與目標(biāo)板的GND連接,讓二者共地。2.選擇需要采樣的信號(hào),這里就是AT24C16的SDA和SCL,將SDA接入邏輯分析儀的通道1(Input1),SCL接入通道1(Input2)。3.將邏輯分析儀和電腦USB口連接,windows會(huì)識(shí)別該設(shè)備,并在屏幕右下角顯示USB設(shè)備標(biāo)識(shí)。ONFI v4協(xié)議分析儀/訓(xùn)練器找歐奧!

圖1邏輯分析儀根據(jù)其硬件設(shè)備的功能和復(fù)雜程度,主要分為式(單機(jī)型)邏輯分析儀和基于電腦(PC-Base)的虛擬邏輯分析儀兩大類。式邏輯分析儀是將所有的軟件,硬件整合在一臺(tái)儀器中,使用方便。虛擬邏輯分析儀則需要結(jié)合電腦使用,利用PC強(qiáng)大的計(jì)算和顯示功能,完成數(shù)據(jù)處理和顯示等工作。專業(yè)邏輯分析儀,通常具有數(shù)量眾多的采樣通道,超快的采樣速度和大容量的存儲(chǔ)深度,但昂貴的價(jià)格也不是個(gè)人所能承受的。作為工程師手頭常備的開發(fā)工具,目前有許多入門級(jí)的邏輯分析儀設(shè)計(jì)。歐奧電子是Prodigy在中國(guó)區(qū)的官方授權(quán)合作伙伴,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測(cè)試解決方案不會(huì)收到EAR進(jìn)出口方面的管制。同時(shí)還有代理其他總類的協(xié)議分析儀,包括嵌入式設(shè)備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓(xùn)練器,I3C協(xié)議分析儀及訓(xùn)練器,RFFE協(xié)議分析儀及訓(xùn)練器等等。我司還有代理SPMI協(xié)議分析儀及訓(xùn)練器,車載以太網(wǎng)分析儀,以及各種相關(guān)的基于示波器的解碼軟件和SI測(cè)試軟件。同時(shí),歐奧電子也有提供高難度焊接,以及高速信號(hào),如UFS,DDR3/DDR4,USBtypeC等高速協(xié)議抓取和分析的服務(wù)。整體功能雖然不能和專業(yè)儀器相比,但是用較低的成本來實(shí)現(xiàn)特定的功能,也是非常成功的設(shè)計(jì)。DigRF v4邏輯分析儀/訓(xùn)練器找歐奧!江門I2C/SPI協(xié)議分析儀價(jià)格

FlexRay邏輯分析儀/訓(xùn)練器找歐奧!汕頭RFFE協(xié)議分析儀那家好

DDR3/DDR4,USBtypeC等高速協(xié)議抓取和分析的服務(wù)。這種類型的時(shí)鐘計(jì)時(shí)會(huì)使邏輯分析儀中的數(shù)據(jù)采樣與被測(cè)設(shè)備中的時(shí)鐘異步。具體來講:定時(shí)分析儀適用于顯示信號(hào)活動(dòng)“相當(dāng)于其他信號(hào)”“何時(shí)”發(fā)生。定時(shí)分析儀側(cè)重于查看各個(gè)信號(hào)之間的時(shí)序關(guān)系,而不是與被測(cè)設(shè)備中控制執(zhí)行的信號(hào)之間的時(shí)序關(guān)系。這就是為什么定時(shí)分析儀可以對(duì)與被測(cè)設(shè)備時(shí)鐘信號(hào)“不同步”或異步的數(shù)據(jù)進(jìn)行采樣。在定時(shí)采集模式下,邏輯分析儀的工作是對(duì)輸入波形進(jìn)行采樣,從而確定它們是高電平還是低電平。為了確定高低,邏輯分析儀會(huì)將輸入信號(hào)的電壓電平與用戶定義的電壓閾值進(jìn)行比較。如果采樣時(shí)信號(hào)高于閾值,則分析儀將信號(hào)顯示為1或高。同樣,低于閾值的信號(hào)將顯示為0或低。下圖闡釋了當(dāng)正弦波跨過閾值電平時(shí)邏輯分析儀對(duì)其進(jìn)行采樣的情況。圖2定時(shí)分析采集原理采集之后采樣點(diǎn)被存儲(chǔ)在內(nèi)存中,并用于重建方形數(shù)字波形。這種要使一切變成方形的處理方式似乎會(huì)限制定時(shí)分析儀的用處。不過定時(shí)分析儀本來也不是打算用作參數(shù)儀器的。若要查看信號(hào)的上升時(shí)間,可以使用示波器。若需校驗(yàn)幾個(gè)或幾百個(gè)信號(hào)之間的時(shí)序關(guān)系,對(duì)其同時(shí)進(jìn)行查看,則定時(shí)分析儀才是正確的選擇。汕頭RFFE協(xié)議分析儀那家好

- 常州RFFE協(xié)議分析儀價(jià)格 2025-07-26

- 梅州I2C/SPI邏輯分析儀電話 2025-07-26

- 佛山I2C/SPI邏輯分析儀那家好 2025-07-26

- 常州UART邏輯分析儀電話 2025-07-26

- 云浮SD協(xié)議分析儀售價(jià) 2025-07-26

- 西安I3C邏輯分析儀電話 2025-07-26

- 上海UFS協(xié)議分析儀報(bào)價(jià) 2025-07-26

- 揭陽RFFE邏輯分析儀品牌 2025-07-26

- 陽江EMMC邏輯分析儀報(bào)價(jià) 2025-07-26

- 韶關(guān)PCIE協(xié)議分析儀價(jià)格 2025-07-26

- 南京風(fēng)壓型變送器現(xiàn)貨 2025-07-26

- 數(shù)字智能儀表XST-262生產(chǎn) 2025-07-26

- 常州節(jié)能ABB接觸器現(xiàn)貨 2025-07-26

- 提供三次元影像測(cè)量?jī)x維保 2025-07-26

- 上海水質(zhì)監(jiān)測(cè)儀 2025-07-26

- 天津傳感器稱重模塊報(bào)價(jià) 2025-07-26

- 制造工業(yè)自動(dòng)化再生資源金屬能譜儀在線自動(dòng)化解決方案 2025-07-26

- 福建是什么顯微CT推薦咨詢 2025-07-26

- 江蘇開關(guān)柜局放檢測(cè)技術(shù)服務(wù) 2025-07-26

- 天津熒光近紅外二區(qū)熒光寬場(chǎng)成像系統(tǒng)答疑解惑 2025-07-26