-

倉儲(chǔ)燈廠家安裝指導(dǎo)服務(wù):助力倉儲(chǔ)照明高效落地

-

高天棚燈:工業(yè)與商業(yè)照明領(lǐng)域的優(yōu)勢之選

-

因庫制宜:倉儲(chǔ)燈照明解決方案的靈活調(diào)整策略

-

消防智能照明燈:火災(zāi)中的“安全導(dǎo)航系統(tǒng)”

-

廠房倉儲(chǔ)燈:依倉庫大小精確擇“光”指南

-

物流燈安裝方式全解析:場景適配與技術(shù)創(chuàng)新

-

庫房倉儲(chǔ)燈如何滿足特殊物品的照明需求

-

倉儲(chǔ)燈安裝高度對照明效果的影響分析

-

高天棚燈照明效果隨高度變化的科學(xué)解析:從光效衰減到空間適配性

-

高效倉儲(chǔ)燈:能源成本節(jié)省的“節(jié)能先鋒”

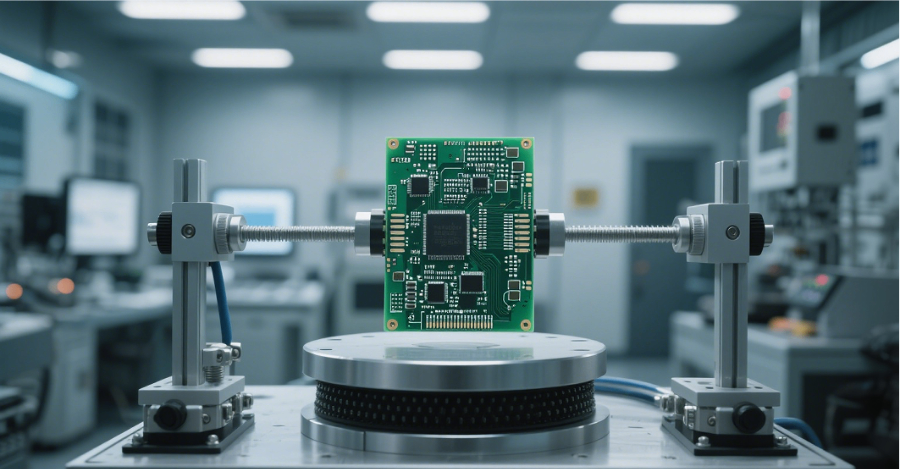

江蘇專業(yè)FPGA開發(fā)硬件開發(fā)供應(yīng)商

在硬件開發(fā)過程中,專業(yè)的設(shè)計(jì)工具是工程師的得力助手,能夠提升開發(fā)效率與設(shè)計(jì)準(zhǔn)確性。EDA 工具是硬件設(shè)計(jì)的,如 Altium Designer、Cadence Allegro 等,它們集成了原理圖設(shè)計(jì)、PCB 布局布線、信號完整性分析等功能。工程師通過原理圖設(shè)計(jì)模塊繪制電路連接關(guān)系,系統(tǒng)可自動(dòng)檢查電氣規(guī)則錯(cuò)誤,避免因設(shè)計(jì)疏漏導(dǎo)致的問題;在 PCB 設(shè)計(jì)階段,工具提供智能布線功能,能根據(jù)設(shè)定規(guī)則自動(dòng)完成走線,并進(jìn)行阻抗計(jì)算和調(diào)整,確保信號完整性。此外,3D 建模軟件如 SolidWorks、AutoCAD,可用于機(jī)械結(jié)構(gòu)設(shè)計(jì),幫助工程師直觀地驗(yàn)證產(chǎn)品外形和裝配關(guān)系,避免機(jī)械干涉問題。熱仿真軟件如 ANSYS Icepak,能模擬設(shè)備的散熱情況,提前發(fā)現(xiàn)散熱瓶頸,優(yōu)化散熱設(shè)計(jì)方案。借助這些專業(yè)工具,工程師可以在虛擬環(huán)境中完成設(shè)計(jì)驗(yàn)證,減少實(shí)物原型制作次數(shù),縮短開發(fā)周期,同時(shí)提高設(shè)計(jì)的準(zhǔn)確性和可靠性,降低開發(fā)成本。?長鴻華晟在硬件可靠性評估中,通過電氣特性測試等多種手段,評估硬件可靠性。江蘇專業(yè)FPGA開發(fā)硬件開發(fā)供應(yīng)商

原理圖設(shè)計(jì)是硬件開發(fā)的起點(diǎn),它將產(chǎn)品的功能需求轉(zhuǎn)化為具體的電路連接關(guān)系,為后續(xù)的 PCB 設(shè)計(jì)、元器件選型等工作奠定基礎(chǔ)。在原理圖設(shè)計(jì)過程中,工程師需要根據(jù)產(chǎn)品的功能要求,選擇合適的芯片、電阻、電容等元器件,并確定它們之間的連接方式。例如,在設(shè)計(jì)一款無線通信模塊的原理圖時(shí),要根據(jù)通信協(xié)議的要求,選擇合適的無線芯片,設(shè)計(jì)天線匹配電路、電源電路、數(shù)據(jù)接口電路等。原理圖設(shè)計(jì)的準(zhǔn)確性和合理性直接影響到整個(gè)硬件系統(tǒng)的性能和穩(wěn)定性。如果原理圖設(shè)計(jì)存在錯(cuò)誤,可能會(huì)導(dǎo)致 PCB 設(shè)計(jì)錯(cuò)誤,進(jìn)而影響產(chǎn)品的功能實(shí)現(xiàn)。而且,一旦在后續(xù)階段發(fā)現(xiàn)原理圖設(shè)計(jì)問題,修改起來不僅耗時(shí)耗力,還可能增加成本。因此,在硬件開發(fā)過程中,原理圖設(shè)計(jì)必須嚴(yán)謹(jǐn)細(xì)致,經(jīng)過反復(fù)檢查和驗(yàn)證,確保電路原理的正確性。河北電路板焊接哪家好硬件開發(fā)費(fèi)用是多少長鴻華晟設(shè)計(jì)系統(tǒng)電路圖和原理圖時(shí),嚴(yán)謹(jǐn)細(xì)致,確保電路的合理性與可靠性。

隨著全球環(huán)保意識的增強(qiáng)和環(huán)保法規(guī)的日益嚴(yán)格,硬件開發(fā)必須將環(huán)保要求納入重要考量,選用綠色環(huán)保的元器件成為必然趨勢。歐盟的 RoHS 指令(限制在電子電氣設(shè)備中使用某些有害物質(zhì)指令)明確限制了鉛、汞、鎘等有害物質(zhì)在電子產(chǎn)品中的使用,企業(yè)若違反將面臨高額罰款和市場禁入。在硬件開發(fā)過程中,工程師需優(yōu)先選擇符合 RoHS、REACH(化學(xué)品注冊、評估、授權(quán)和限制)等環(huán)保標(biāo)準(zhǔn)的元器件,如無鉛焊料、無鹵阻燃材料等。此外,選擇可回收材料制作產(chǎn)品外殼,采用低能耗的制造工藝,也是踐行環(huán)保理念的重要舉措。以智能手機(jī)為例,廠商通過使用可回收的鋁合金外殼、無汞的液晶顯示屏,以及優(yōu)化生產(chǎn)流程降低能耗,既滿足了環(huán)保要求,又提升了品牌形象,迎合了消費(fèi)者對綠色產(chǎn)品的需求。關(guān)注環(huán)保要求不僅是企業(yè)履行社會(huì)責(zé)任的體現(xiàn),也有助于企業(yè)開拓國際市場,增強(qiáng)市場競爭力。?

在現(xiàn)代電子產(chǎn)品中,硬件和軟件是相互依存、密不可分的。硬件開發(fā)團(tuán)隊(duì)負(fù)責(zé)設(shè)計(jì)和實(shí)現(xiàn)產(chǎn)品的物理架構(gòu),提供運(yùn)行軟件的硬件平臺;軟件團(tuán)隊(duì)則根據(jù)硬件的特性和功能需求,開發(fā)相應(yīng)的程序,實(shí)現(xiàn)產(chǎn)品的各種功能。兩者只有緊密協(xié)作,才能實(shí)現(xiàn)軟硬協(xié)同,打造出性能優(yōu)異的產(chǎn)品。例如,在開發(fā)一款智能音箱時(shí),硬件團(tuán)隊(duì)設(shè)計(jì)好音箱的音頻電路、無線通信模塊等硬件部分,軟件團(tuán)隊(duì)則開發(fā)語音識別、音樂播放控制等軟件程序。在開發(fā)過程中,硬件團(tuán)隊(duì)需要及時(shí)向軟件團(tuán)隊(duì)提供硬件的接口規(guī)范、性能參數(shù)等信息,軟件團(tuán)隊(duì)則根據(jù)硬件的實(shí)際情況進(jìn)行程序優(yōu)化和調(diào)試。如果雙方溝通不暢,可能會(huì)出現(xiàn)軟件與硬件不兼容的問題,影響產(chǎn)品的功能實(shí)現(xiàn)和用戶體驗(yàn)。因此,硬件開發(fā)團(tuán)隊(duì)與軟件團(tuán)隊(duì)的緊密協(xié)作是實(shí)現(xiàn)軟硬協(xié)同,確保產(chǎn)品成功的關(guān)鍵。長鴻華晟注重硬件開發(fā)過程中的溝通協(xié)作,團(tuán)隊(duì)成員密切配合,保障項(xiàng)目順利推進(jìn)。

硬件產(chǎn)品從研發(fā)、上市到退出市場,其生命周期受技術(shù)更新、市場需求變化等多種因素影響。通過持續(xù)優(yōu)化硬件設(shè)計(jì)和性能,可有效延長產(chǎn)品生命周期,為企業(yè)創(chuàng)造更大價(jià)值。在產(chǎn)品上市后,企業(yè)可根據(jù)用戶反饋和市場需求,對硬件進(jìn)行功能升級和性能優(yōu)化。例如,智能手機(jī)廠商通過優(yōu)化電源管理芯片的算法,提升電池續(xù)航能力;改進(jìn)攝像頭的硬件電路和圖像處理算法,增強(qiáng)拍照效果。此外,隨著制造工藝的進(jìn)步和元器件成本的降低,對硬件進(jìn)行成本優(yōu)化也是延長生命周期的重要手段,如采用更先進(jìn)的封裝工藝減小 PCB 尺寸,替換價(jià)格下降的高性能元器件提升產(chǎn)品性價(jià)比。在技術(shù)層面,持續(xù)關(guān)注行業(yè)新技術(shù)的發(fā)展,適時(shí)將新技術(shù)融入產(chǎn)品,如在智能設(shè)備中引入 AI 加速芯片提升運(yùn)算能力。通過不斷地功能優(yōu)化、性能提升和成本控制,硬件產(chǎn)品能夠保持市場競爭力,滿足用戶日益增長的需求,從而在市場上保持較長的生命周期,為企業(yè)帶來持續(xù)的經(jīng)濟(jì)效益。長鴻華晟在原理圖設(shè)計(jì)中,借鑒芯片廠家的參考設(shè)計(jì),同時(shí)融入自身創(chuàng)新。天津電路板焊接硬件開發(fā)節(jié)能規(guī)范

在硬件方案制定中,長鴻華晟的工程師綜合考量技術(shù)可行性、可靠性與成本,全力尋找關(guān)鍵器件與技術(shù)支持。江蘇專業(yè)FPGA開發(fā)硬件開發(fā)供應(yīng)商

時(shí)鐘電路為硬件系統(tǒng)提供基準(zhǔn)時(shí)鐘信號,如同整個(gè)系統(tǒng)的 “心臟起搏器”,控制著各個(gè)模塊的運(yùn)行節(jié)奏,是系統(tǒng)實(shí)現(xiàn)同步運(yùn)行的基礎(chǔ)。在數(shù)字電路中,時(shí)鐘信號決定了數(shù)據(jù)的傳輸速率和處理周期,時(shí)鐘信號的穩(wěn)定性和準(zhǔn)確性直接影響系統(tǒng)性能。常見的時(shí)鐘電路包括晶體振蕩器、鎖相環(huán)(PLL)等。晶體振蕩器利用石英晶體的壓電效應(yīng)產(chǎn)生穩(wěn)定的振蕩信號,為系統(tǒng)提供基本時(shí)鐘頻率;鎖相環(huán)則可對時(shí)鐘信號進(jìn)行倍頻或分頻處理,滿足不同模塊對時(shí)鐘頻率的需求。在多核處理器的硬件開發(fā)中,精確的時(shí)鐘同步至關(guān)重要,若各的時(shí)鐘信號存在微小偏差,會(huì)導(dǎo)致數(shù)據(jù)處理錯(cuò)誤和系統(tǒng)不穩(wěn)定。此外,在通信設(shè)備中,時(shí)鐘電路的抖動(dòng)(Jitter)指標(biāo)直接影響信號傳輸?shù)臏?zhǔn)確性,抖動(dòng)過大可能導(dǎo)致數(shù)據(jù)誤碼率升高。因此,在硬件開發(fā)中,需精心設(shè)計(jì)時(shí)鐘電路,合理選擇時(shí)鐘芯片和布局布線,減少時(shí)鐘信號的干擾和損耗,確保整個(gè)硬件系統(tǒng)能夠穩(wěn)定、同步地運(yùn)行。?江蘇專業(yè)FPGA開發(fā)硬件開發(fā)供應(yīng)商

- 安徽電路板電子元器件/PCB電路板費(fèi)用是多少 2025-07-09

- 北京電路板電子元器件/PCB電路板性能 2025-07-09

- 浙江北京硬件開發(fā)硬件開發(fā)詢問報(bào)價(jià) 2025-07-09

- 上海視頻AI算法硬件開發(fā)費(fèi)用 2025-07-08

- 安徽oem電子元器件/PCB電路板標(biāo)準(zhǔn) 2025-07-08

- 上海智能硬件開發(fā)咨詢報(bào)價(jià) 2025-07-08

- 江蘇oem電子元器件/PCB電路板智能系統(tǒng) 2025-07-08

- 電路板電子元器件/PCB電路板設(shè)計(jì) 2025-07-08

- 山東電路板開發(fā)制作硬件開發(fā)報(bào)價(jià) 2025-07-08

- 江蘇北京電路板焊接硬件開發(fā) 2025-07-08

- 橋堆不同型號有何區(qū)別 2025-07-09

- 日照氧化鋯陶瓷棒廠家 2025-07-09

- 電機(jī)和MCU驅(qū)動(dòng)系統(tǒng)卡扣式防水透氣塞 2025-07-09

- 電鍍電源igbt模塊IGBT IPM智能型功率模塊 2025-07-09

- 上海電感電子元器件鍍金貴金屬 2025-07-09

- 標(biāo)準(zhǔn)AH402F貨源充足 2025-07-09

- OS02G10攝像頭模組 2025-07-09

- 長寧區(qū)質(zhì)量機(jī)械電氣設(shè)備報(bào)價(jià) 2025-07-09

- 紹興瞬變抑制二極管分類 2025-07-09

- 嘉興電木ksd301溫控器 2025-07-09