上海ICP材料刻蝕加工

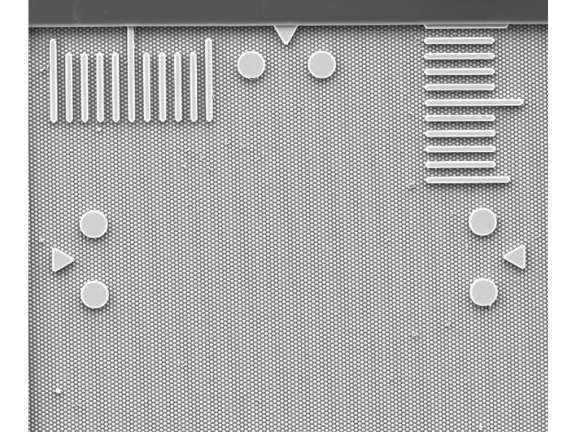

ICP材料刻蝕作為一種高效的微納加工技術(shù),在材料科學(xué)領(lǐng)域發(fā)揮著重要作用。該技術(shù)通過精確控制等離子體的能量和化學(xué)反應(yīng)條件,能夠?qū)崿F(xiàn)對(duì)多種材料的精確刻蝕。無論是金屬、半導(dǎo)體還是絕緣體材料,ICP刻蝕都能展現(xiàn)出良好的加工效果。在集成電路制造中,ICP刻蝕技術(shù)被普遍應(yīng)用于柵極、接觸孔、通孔等關(guān)鍵結(jié)構(gòu)的加工。同時(shí),該技術(shù)還適用于制備微納結(jié)構(gòu)的光學(xué)元件、生物傳感器等器件。ICP刻蝕技術(shù)的發(fā)展不只推動(dòng)了微電子技術(shù)的進(jìn)步,也為其他領(lǐng)域的科學(xué)研究和技術(shù)創(chuàng)新提供了有力支持。MEMS材料刻蝕技術(shù)提升了微傳感器的靈敏度。上海ICP材料刻蝕加工

隨著科學(xué)技術(shù)的不斷進(jìn)步和創(chuàng)新,材料刻蝕技術(shù)將呈現(xiàn)出更加多元化、智能化的發(fā)展趨勢(shì)。一方面,隨著新材料、新工藝的不斷涌現(xiàn),如柔性電子材料、生物相容性材料等,將對(duì)材料刻蝕技術(shù)提出更高的要求和挑戰(zhàn)。為了滿足這些需求,研究人員將不斷探索新的刻蝕方法和工藝,如采用更高效的等離子體源、開發(fā)更先進(jìn)的刻蝕氣體配比等。另一方面,隨著人工智能、大數(shù)據(jù)等技術(shù)的不斷發(fā)展,材料刻蝕過程將實(shí)現(xiàn)更加智能化的控制和優(yōu)化。通過引入先進(jìn)的傳感器和控制系統(tǒng),可以實(shí)時(shí)監(jiān)測(cè)刻蝕過程中的關(guān)鍵參數(shù)和指標(biāo),并根據(jù)反饋信息進(jìn)行實(shí)時(shí)調(diào)整和優(yōu)化,從而提高刻蝕效率和產(chǎn)品質(zhì)量。江蘇氧化硅材料刻蝕加工工廠離子束刻蝕通過創(chuàng)新的深腔加工技術(shù)實(shí)現(xiàn)MEMS陀螺儀的性能躍升。

材料刻蝕技術(shù)是半導(dǎo)體制造過程中不可或缺的一環(huán)。它決定了晶體管、電容器等關(guān)鍵元件的尺寸、形狀和位置,從而直接影響半導(dǎo)體器件的性能和可靠性。隨著半導(dǎo)體技術(shù)的不斷發(fā)展,對(duì)材料刻蝕技術(shù)的要求也越來越高。從早期的濕法刻蝕到現(xiàn)在的干法刻蝕(如ICP刻蝕),材料刻蝕技術(shù)經(jīng)歷了巨大的變革。這些變革不只提高了刻蝕的精度和效率,還降低了對(duì)環(huán)境的污染和對(duì)材料的損傷。ICP刻蝕技術(shù)作為當(dāng)前比較先進(jìn)的材料刻蝕技術(shù)之一,以其高精度、高效率和高選擇比的特點(diǎn),在半導(dǎo)體制造中發(fā)揮著越來越重要的作用。未來,隨著半導(dǎo)體技術(shù)的不斷進(jìn)步和創(chuàng)新,材料刻蝕技術(shù)將繼續(xù)帶領(lǐng)半導(dǎo)體產(chǎn)業(yè)的發(fā)展潮流。

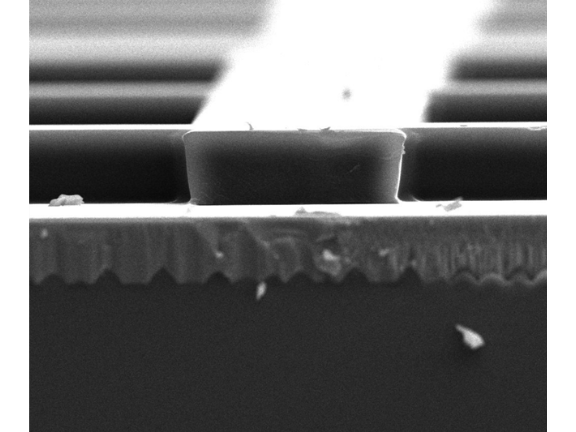

MEMS慣性傳感器領(lǐng)域依賴離子束刻蝕實(shí)現(xiàn)性能突破,其創(chuàng)新的深寬比控制技術(shù)解決高精度陀螺儀制造的痛點(diǎn)。通過建立雙離子源協(xié)同作用機(jī)制,在硅基底加工出深寬比超過25:1的微柱陣列結(jié)構(gòu)。該工藝的重心突破在于發(fā)展出智能終端檢測(cè)系統(tǒng)與自補(bǔ)償算法,使諧振結(jié)構(gòu)的熱漂移系數(shù)降至十億分之一級(jí)別,為自動(dòng)駕駛系統(tǒng)提供超越衛(wèi)星精度的慣性導(dǎo)航模塊。中性束刻蝕技術(shù)開啟介電材料加工新紀(jì)元,其獨(dú)特的粒子中性化機(jī)制徹底解決柵氧化層電荷損傷問題。在3nm邏輯芯片制造中,該技術(shù)創(chuàng)造性地保持原子級(jí)柵極界面完整性,使電子遷移率提升兩倍。主要技術(shù)突破在于發(fā)展出能量分散控制模塊,在納米鰭片加工中完美維持介電材料的晶體結(jié)構(gòu),為集成電路微縮提供原子級(jí)無損加工工藝路線。硅材料刻蝕技術(shù)優(yōu)化了集成電路的可靠性。

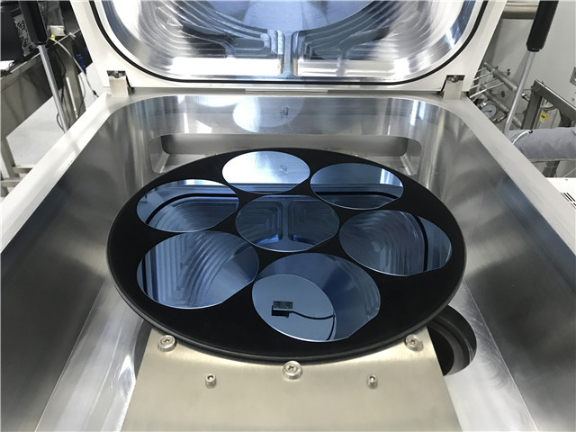

先進(jìn)封裝是指一種用于提高集成電路(IC)的性能、功能和可靠性的技術(shù),它通過將不同的IC或器件以物理或電氣的方式連接起來,形成一個(gè)更小、更快、更強(qiáng)的系統(tǒng)。深硅刻蝕設(shè)備是一種用于制造高縱橫比硅結(jié)構(gòu)的先進(jìn)工藝設(shè)備,它在先進(jìn)封裝中主要用于實(shí)現(xiàn)通過硅通孔(TSV)或硅中介層(SiP)等技術(shù)的三維堆疊或異質(zhì)集成。深硅刻蝕設(shè)備與先進(jìn)封裝的關(guān)系是密切而重要的,深硅刻蝕設(shè)備為先進(jìn)封裝提供了高效率、高精度和高靈活性的制造工具,而先進(jìn)封裝為深硅刻蝕設(shè)備提供了廣闊的應(yīng)用領(lǐng)域和市場(chǎng)需求。硅濕法刻蝕相對(duì)于干法刻蝕是一種相對(duì)簡(jiǎn)單且成本較低的方法,通常在室溫下使用液體刻蝕介質(zhì)進(jìn)行。遼寧MEMS材料刻蝕服務(wù)

氮化鎵材料刻蝕提高了LED芯片的性能。上海ICP材料刻蝕加工

硅材料刻蝕是集成電路制造過程中不可或缺的一環(huán)。它決定了晶體管、電容器等關(guān)鍵元件的尺寸、形狀和位置,從而直接影響集成電路的性能和可靠性。隨著集成電路特征尺寸的不斷縮小,對(duì)硅材料刻蝕技術(shù)的要求也越來越高。ICP刻蝕技術(shù)以其高精度、高效率和高選擇比的特點(diǎn),成為滿足這些要求的關(guān)鍵技術(shù)之一。通過精確控制等離子體的能量和化學(xué)反應(yīng)條件,ICP刻蝕可以實(shí)現(xiàn)對(duì)硅材料的精確刻蝕,制備出具有優(yōu)異性能的集成電路。此外,ICP刻蝕技術(shù)還能處理復(fù)雜的三維結(jié)構(gòu),為集成電路的小型化、集成化和高性能化提供了有力支持。可以說,硅材料刻蝕技術(shù)的發(fā)展是推動(dòng)集成電路技術(shù)進(jìn)步的關(guān)鍵因素之一。上海ICP材料刻蝕加工

- 黑龍江MEMS材料刻蝕服務(wù) 2025-07-29

- 安徽氮化鎵材料刻蝕廠家 2025-07-28

- 云南氮化鎵材料刻蝕多少錢 2025-07-28

- 甘肅GaN材料刻蝕加工廠 2025-07-28

- 陶瓷靶材磁控濺射平臺(tái) 2025-07-28

- 江西MEMS材料刻蝕服務(wù) 2025-07-28

- 遼寧氧化硅材料刻蝕加工 2025-07-28

- 四川ICP材料刻蝕服務(wù) 2025-07-28

- 河南專業(yè)磁控濺射用處 2025-07-28

- 重慶MEMS材料刻蝕加工 2025-07-28

- 黃浦區(qū)智能GSM模塊銷售 2025-07-29

- 江寧區(qū)國產(chǎn)半導(dǎo)體器件 2025-07-29

- rainbow冷暖機(jī)溫控器愛采購 2025-07-29

- 江蘇雷達(dá)物位計(jì)傳感器廠家供應(yīng) 2025-07-29

- 江蘇PET層間附著力涂液技術(shù) 2025-07-29

- 四川空調(diào)電容器技術(shù)規(guī)范 2025-07-29

- 平頂山弧形釹鐵硼磁鋼 2025-07-29

- 崇明區(qū)挑選無線通信模塊解決方案廠家報(bào)價(jià) 2025-07-29

- HDF657E5-S6 2025-07-29

- 湖南阻燃防水接頭定做 2025-07-29