山東安路FPGA開發(fā)板交流

基于FPGA開發(fā)板進行項目開發(fā)時,軟件工具鏈起著關(guān)鍵作用。以Altera(現(xiàn)Intel)的QuartusPrime軟件為例,其提供了完整的FPGA開發(fā)流程支持。在設(shè)計輸入階段,開發(fā)者既可以使用硬件描述語言Verilog或VHDL編寫代碼,描述電路的邏輯功能;也可以采用原理圖輸入方式,通過圖形化的方式搭建電路模塊,直觀展示設(shè)計架構(gòu)。完成設(shè)計輸入后,QuartusPrime的綜合功能會將代碼或原理圖轉(zhuǎn)換為門級網(wǎng)表,針對目標(biāo)FPGA芯片的邏輯資源進行優(yōu)化映射。接著是布局布線環(huán)節(jié),軟件根據(jù)芯片的物理結(jié)構(gòu),合理安排邏輯單元的位置,并完成各單元之間的連線,確保信號傳輸?shù)臏?zhǔn)確性與穩(wěn)定性。通過編程下載功能,將生成的配置文件燒錄到FPGA開發(fā)板中,使設(shè)計在硬件上得以實現(xiàn)。同時,該軟件還提供了仿真功能,方便開發(fā)者在硬件實現(xiàn)前對設(shè)計進行功能驗證,減少開發(fā)過程中的錯誤與風(fēng)險。 預(yù)算有限時,優(yōu)先挑選具備豐富教程、價格親民的經(jīng)典入門級 FPGA 開發(fā)板較為合適。山東安路FPGA開發(fā)板交流

外設(shè)接口是FPGA開發(fā)板與外部世界連接的橋梁,賦予了開發(fā)板強大的拓展能力。通用輸入輸出接口(GPIO)具有極高的靈活性,通過編程可以將其配置為輸入或輸出模式,用于連接各類傳感器和執(zhí)行器。比如連接溫度傳感器獲取環(huán)境溫度數(shù)據(jù),或者連接LED燈實現(xiàn)不同的燈光顯示效果。UART接口實現(xiàn)了開發(fā)板與其他設(shè)備之間的串行通信,常用于與計算機進行數(shù)據(jù)傳輸和指令交互,方便開發(fā)者進行程序下載和調(diào)試。SPI和I2C接口則適用于與外部芯片進行高速穩(wěn)定的數(shù)據(jù)通信,可連接EEPROM、ADC等芯片,實現(xiàn)數(shù)據(jù)的存儲和模擬信號的采集。以太網(wǎng)接口的存在使開發(fā)板具備了網(wǎng)絡(luò)通信能力,能夠接入局域網(wǎng)或互聯(lián)網(wǎng),在物聯(lián)網(wǎng)應(yīng)用中,可以實現(xiàn)設(shè)備之間的數(shù)據(jù)交互和遠程數(shù)據(jù)傳輸,極大地拓展了FPGA開發(fā)板的應(yīng)用范圍。 上海安路FPGA開發(fā)板論壇想實現(xiàn)網(wǎng)絡(luò)通信,集成千兆以太網(wǎng)接口、采用 RGMII 接口的 FPGA 開發(fā)板可作為優(yōu)先考慮。

FPGA 開發(fā)板的開源社區(qū)為開發(fā)者提供了豐富的資源與交流平臺。眾多開發(fā)者在開源社區(qū)分享基于開發(fā)板的設(shè)計項目,涵蓋從基礎(chǔ)的 LED 閃爍、數(shù)碼管顯示,到復(fù)雜的圖像處理、通信協(xié)議實現(xiàn)等各類案例。這些開源項目不僅包含完整的代碼,還附有詳細的設(shè)計文檔與說明,開發(fā)者可從中學(xué)習(xí)新的技術(shù)與開發(fā)思路。同時,開發(fā)者也可將自己的項目成果分享到社區(qū),與其他開發(fā)者交流合作,共同解決開發(fā)過程中遇到的問題。開源社區(qū)的存在促進了技術(shù)的共享與創(chuàng)新,降低了開發(fā)門檻,讓更多開發(fā)者能夠參與到 FPGA 技術(shù)的研究與應(yīng)用中,推動 FPGA 開發(fā)板在各個領(lǐng)域的廣泛應(yīng)用。

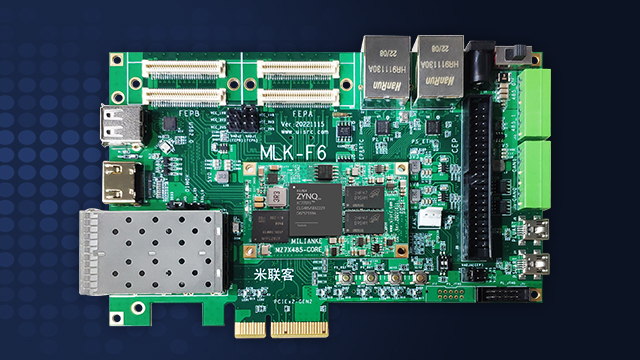

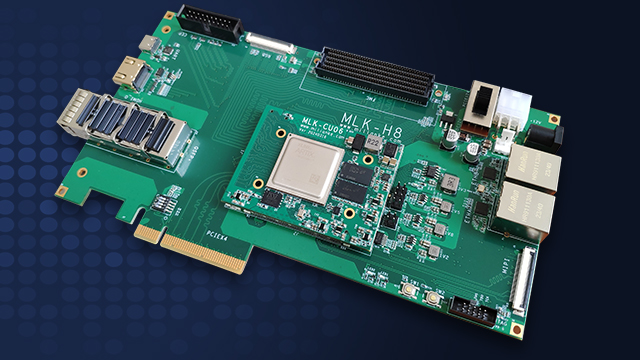

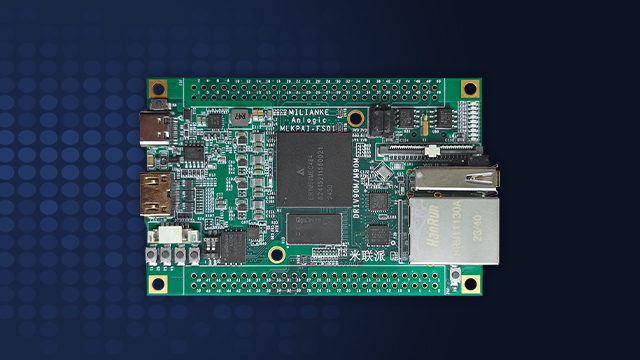

FPGA開發(fā)板作為數(shù)字電路設(shè)計的重要實踐平臺,其硬件架構(gòu)融合了多種關(guān)鍵組件。以常見的XilinxArtix-7系列開發(fā)板為例,F(xiàn)PGA芯片是整個系統(tǒng)的關(guān)鍵器件,像XC7A100T型號芯片,擁有豐富的邏輯單元、DSP切片和BlockRAM資源,能夠滿足復(fù)雜數(shù)字系統(tǒng)的設(shè)計需求。開發(fā)板上配備的電源管理模塊,通過多級電壓轉(zhuǎn)換電路,為FPGA芯片及其他外設(shè)提供穩(wěn)定的供電,例如將外部輸入的5V電壓轉(zhuǎn)換為、等不同電壓等級,確保各部件正常運行。復(fù)位電路在啟動或異常情況下能回到初始狀態(tài),晶振電路為系統(tǒng)提供精確的時鐘信號,使FPGA內(nèi)部邏輯單元能夠按照預(yù)定節(jié)奏工作。此外,開發(fā)板還集成了豐富的接口,包括USB、以太網(wǎng)、SPI、I2C等,方便與外部設(shè)備進行數(shù)據(jù)交互和通信,這些硬件資源共同構(gòu)成了FPGA開發(fā)板穩(wěn)定運行的基礎(chǔ)環(huán)境。 FPGA 開發(fā)板的版本迭代,帶來性能提升與功能增強。

FPGA開發(fā)板在教育教學(xué)中具有重要的價值。對于高校電子信息類的學(xué)生而言,開發(fā)板是將理論知識轉(zhuǎn)化為實踐能力的重要媒介。在數(shù)字電路課程學(xué)習(xí)中,學(xué)生通過在開發(fā)板上實現(xiàn)簡單的邏輯電路,如計數(shù)器、譯碼器等,直觀地理解數(shù)字電路的工作原理與設(shè)計方法。在學(xué)習(xí)硬件描述語言時,學(xué)生利用開發(fā)板進行實際項目練習(xí),從簡單的LED閃爍到復(fù)雜的數(shù)碼管動態(tài)顯示,逐步掌握Verilog或VHDL語言的編程技巧。在綜合性課程設(shè)計與畢業(yè)設(shè)計中,開發(fā)板更是學(xué)生展示創(chuàng)新能力的平臺。學(xué)生可以基于開發(fā)板開展如智能小車設(shè)計、簡易數(shù)字示波器制作等項目,綜合運用多門課程所學(xué)知識,鍛煉系統(tǒng)設(shè)計、調(diào)試與優(yōu)化的能力,培養(yǎng)學(xué)生的工程實踐素養(yǎng)與創(chuàng)新思維,為未來從事電子信息相關(guān)行業(yè)的工作奠定堅實的基礎(chǔ)。 物聯(lián)網(wǎng)應(yīng)用中,F(xiàn)PGA 開發(fā)板連接傳感器與設(shè)備,構(gòu)建智能互聯(lián)系統(tǒng)。山東入門級FPGA開發(fā)板學(xué)習(xí)步驟

FPGA 開發(fā)板豐富的存儲資源,為數(shù)據(jù)處理提供有力支撐。山東安路FPGA開發(fā)板交流

FPGA 開發(fā)板的軟件生態(tài)同樣豐富,為開發(fā)者提供了的支持。在開發(fā)工具方面,Xilinx 的 Vivado 軟件是一款功能強大的開發(fā)套件。它集成了設(shè)計輸入、綜合、實現(xiàn)和調(diào)試等一系列功能。開發(fā)者可以通過硬件描述語言,如 Verilog 或 VHDL,在 Vivado 中進行設(shè)計輸入,將自己的電路設(shè)計思路轉(zhuǎn)化為代碼形式。綜合工具會將這些代碼轉(zhuǎn)化為門級網(wǎng)表,映射到 FPGA 芯片的邏輯資源上。實現(xiàn)過程則負責(zé)將網(wǎng)表布局到 FPGA 芯片位置,并完成布線,確保信號能夠準(zhǔn)確傳輸。功能允許開發(fā)者在實際硬件實現(xiàn)之前,對設(shè)計進行功能驗證,通過設(shè)置輸入激勵,觀察輸出結(jié)果,檢查設(shè)計是否符合預(yù)期,降低了開發(fā)過程中的錯誤。調(diào)試工具則在硬件實現(xiàn)后,幫助開發(fā)者解決可能出現(xiàn)的問題,例如通過邏輯分析儀觀察內(nèi)部信號的變化,找出邏輯錯誤或時序問題。同時,Vivado 還提供了豐富的 IP 核資源,開發(fā)者可以直接調(diào)用這些預(yù)先設(shè)計好的功能模塊,如數(shù)字信號處理模塊、通信協(xié)議模塊等,極大地縮短了開發(fā)周期,提高了開發(fā)效率,讓開發(fā)者能夠更專注于系統(tǒng)級的設(shè)計與創(chuàng)新。山東安路FPGA開發(fā)板交流

- 進口FPGA定制項目工業(yè)模板 2025-07-24

- 初學(xué)FPGA定制項目工業(yè)模板 2025-07-24

- 微型高性價比FPGA工程師 2025-07-24

- 江蘇國產(chǎn)高性價比FPGA 2025-07-24

- 核心板高性價比FPGA資料下載 2025-07-24

- 學(xué)習(xí)FPGA定制項目基礎(chǔ) 2025-07-24

- 進口高性價比FPGA工程師 2025-07-24

- 多功能高性價比FPGA學(xué)習(xí)板 2025-07-24

- 智能高性價比FPGA特點與應(yīng)用 2025-07-24

- 徐州初學(xué)高性價比FPGA 2025-07-24

- 河南低功耗LDO芯片廠家 2025-07-24

- 佛山靜電保護ESD二極管廠家現(xiàn)貨 2025-07-24

- G2PF230VS02 2025-07-24

- 河北電源管理芯片采購 2025-07-24

- 1.25a可恢復(fù)保險絲尺寸 2025-07-24

- 江西輪式電鍍設(shè)備咨詢報價 2025-07-24

- 濰坊放大器生產(chǎn)商 2025-07-24

- 尼龍成型件生產(chǎn) 2025-07-24

- 防潮汽車?yán)^電器廠家 2025-07-24

- 江蘇電加熱控制柜控制柜批發(fā) 2025-07-24