山東開(kāi)發(fā)FPGA開(kāi)發(fā)板模塊

FPGA 開(kāi)發(fā)板在智能安防領(lǐng)域有著深入的應(yīng)用,為社會(huì)安全提供了堅(jiān)實(shí)的技術(shù)支撐。在智能監(jiān)控系統(tǒng)中,開(kāi)發(fā)板除了承擔(dān)視頻處理的任務(wù)外,還能實(shí)現(xiàn)智能行為分析功能。通過(guò)對(duì)監(jiān)控視頻的實(shí)時(shí)分析,開(kāi)發(fā)板能夠識(shí)別出人員的異常行為,如奔跑、摔倒、長(zhǎng)時(shí)間停留等,以及物體的異常移動(dòng),如物品被移動(dòng)、闖入禁區(qū)等。一旦檢測(cè)到異常情況,開(kāi)發(fā)板立即觸發(fā)報(bào)警機(jī)制,向監(jiān)控人員發(fā)送警報(bào)信息,同時(shí)可聯(lián)動(dòng)相關(guān)設(shè)備,如啟動(dòng)錄像、開(kāi)啟警示燈光等。在門(mén)禁系統(tǒng)中,開(kāi)發(fā)板可結(jié)合人臉識(shí)別、指紋識(shí)別等識(shí)別技術(shù),對(duì)人員身份進(jìn)行準(zhǔn)確的驗(yàn)證。通過(guò)與門(mén)禁通信,開(kāi)發(fā)板門(mén)鎖的開(kāi)啟和關(guān)閉,實(shí)現(xiàn)對(duì)人員出入的管理。此外,開(kāi)發(fā)板還能與其他安防設(shè)備,如煙霧報(bào)警器、紅外探測(cè)器等集成,構(gòu)建一個(gè)智能化的安防體系,為公共場(chǎng)所、企業(yè)、家庭等提供可靠的安全防護(hù)。遠(yuǎn)程監(jiān)控系統(tǒng)通過(guò) FPGA 開(kāi)發(fā)板,實(shí)現(xiàn)設(shè)備狀態(tài)的實(shí)時(shí)查看與管理。山東開(kāi)發(fā)FPGA開(kāi)發(fā)板模塊

FPGA開(kāi)發(fā)板在工業(yè)機(jī)器人系統(tǒng)構(gòu)建中具有重要意義。開(kāi)發(fā)板可用于處理機(jī)器人的運(yùn)動(dòng)規(guī)劃算法,根據(jù)任務(wù)要求生成機(jī)器人各關(guān)節(jié)的運(yùn)動(dòng)軌跡。通過(guò)與伺服電機(jī)驅(qū)動(dòng)器進(jìn)行通信,向電機(jī)發(fā)送信號(hào),精確電機(jī)的轉(zhuǎn)速、轉(zhuǎn)矩與位置,從而實(shí)現(xiàn)機(jī)器人的精確運(yùn)動(dòng)。在機(jī)器人的視覺(jué)系統(tǒng)中,開(kāi)發(fā)板負(fù)責(zé)處理攝像頭采集的圖像數(shù)據(jù)。對(duì)圖像進(jìn)行識(shí)別與分析,檢測(cè)目標(biāo)物體的位置、形狀與姿態(tài),為機(jī)器人的抓取、裝配等操作提供準(zhǔn)確的信息。例如,在工業(yè)生產(chǎn)線上,機(jī)器人通過(guò)視覺(jué)系統(tǒng)識(shí)別零部件的位置,開(kāi)發(fā)板根據(jù)識(shí)別結(jié)果規(guī)劃?rùn)C(jī)器人的運(yùn)動(dòng)路徑,機(jī)器人準(zhǔn)確抓取零部件并進(jìn)行裝配。此外,開(kāi)發(fā)板還可以實(shí)現(xiàn)機(jī)器人之間的通信與協(xié)作,使多個(gè)機(jī)器人能夠協(xié)同完成復(fù)雜的生產(chǎn)任務(wù),提高工業(yè)生產(chǎn)的自動(dòng)化水平與生產(chǎn)效率。 吉林開(kāi)發(fā)FPGA開(kāi)發(fā)板學(xué)習(xí)視頻FPGA 開(kāi)發(fā)板助力無(wú)線通信設(shè)備,實(shí)現(xiàn)高效信號(hào)收發(fā)與處理。

對(duì)于電子工程師而言,F(xiàn)PGA開(kāi)發(fā)板是產(chǎn)品原型設(shè)計(jì)階段的重要工具。在新產(chǎn)品研發(fā)初期,工程師需要驗(yàn)證設(shè)計(jì)方案的可行性,F(xiàn)PGA開(kāi)發(fā)板的靈活性和可重構(gòu)性正好滿(mǎn)足這一需求。以設(shè)計(jì)一款新型的工業(yè)數(shù)據(jù)采集設(shè)備為例,工程師可以先在FPGA開(kāi)發(fā)板上搭建硬件平臺(tái),通過(guò)連接各類(lèi)傳感器采集工業(yè)現(xiàn)場(chǎng)的數(shù)據(jù),如溫度、壓力、流量等,并利用FPGA強(qiáng)大的邏輯處理能力對(duì)采集到的數(shù)據(jù)進(jìn)行濾波、轉(zhuǎn)換等預(yù)處理操作。然后,通過(guò)開(kāi)發(fā)板上的通信接口將處理后的數(shù)據(jù)傳輸至其他設(shè)備或上位機(jī)進(jìn)行進(jìn)一步分析。在這個(gè)過(guò)程中,如果發(fā)現(xiàn)設(shè)計(jì)方案存在問(wèn)題,工程師可以方便地對(duì)FPGA的程序進(jìn)行修改和優(yōu)化,而無(wú)需重新設(shè)計(jì)硬件電路,縮短了產(chǎn)品研發(fā)周期,降低了研發(fā)成本,提高了產(chǎn)品研發(fā)的效率和成功率。

FPGA開(kāi)發(fā)板的軟件生態(tài)同樣豐富,為開(kāi)發(fā)者提供了的支持。在開(kāi)發(fā)工具方面,Xilinx的Vivado軟件是一款功能強(qiáng)大且使用的開(kāi)發(fā)套件。它集成了設(shè)計(jì)輸入、綜合、實(shí)現(xiàn)、仿真和調(diào)試等一系列功能。開(kāi)發(fā)者可以通過(guò)硬件描述語(yǔ)言,如Verilog或VHDL,在Vivado中進(jìn)行設(shè)計(jì)輸入,將自己的電路設(shè)計(jì)思路轉(zhuǎn)化為代碼形式。綜合工具會(huì)將這些代碼轉(zhuǎn)化為門(mén)級(jí)網(wǎng)表,映射到FPGA芯片的邏輯資源上。實(shí)現(xiàn)過(guò)程則負(fù)責(zé)將網(wǎng)表布局到FPGA芯片的具置,并完成布線,確保信號(hào)能夠準(zhǔn)確傳輸。仿真功能允許開(kāi)發(fā)者在實(shí)際硬件實(shí)現(xiàn)之前,對(duì)設(shè)計(jì)進(jìn)行功能驗(yàn)證,通過(guò)設(shè)置輸入激勵(lì),觀察輸出結(jié)果,檢查設(shè)計(jì)是否符合預(yù)期,降低了開(kāi)發(fā)過(guò)程中的錯(cuò)誤風(fēng)險(xiǎn)。調(diào)試工具則在硬件實(shí)現(xiàn)后,幫助開(kāi)發(fā)者定位和解決可能出現(xiàn)的問(wèn)題,例如通過(guò)邏輯分析儀觀察內(nèi)部信號(hào)的變化,找出邏輯錯(cuò)誤或時(shí)序問(wèn)題。同時(shí),Vivado還提供了豐富的IP核資源,開(kāi)發(fā)者可以直接調(diào)用這些預(yù)先設(shè)計(jì)好的功能模塊,如數(shù)字信號(hào)處理模塊、通信協(xié)議模塊等,極大地縮短了開(kāi)發(fā)周期,提高了開(kāi)發(fā)效率,讓開(kāi)發(fā)者能夠更專(zhuān)注于系統(tǒng)級(jí)的設(shè)計(jì)與創(chuàng)新。開(kāi)發(fā)者通過(guò) FPGA 開(kāi)發(fā)板,用硬件描述語(yǔ)言將創(chuàng)意轉(zhuǎn)化為實(shí)際硬件功能。

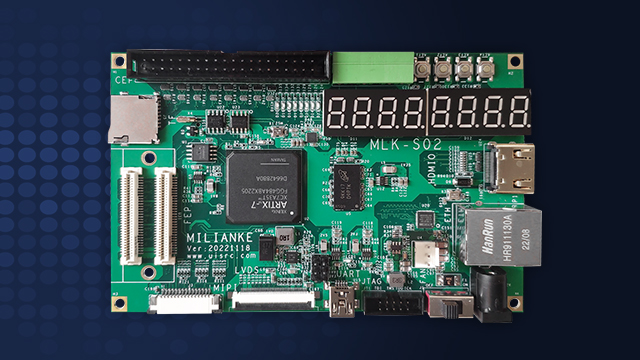

FPGA開(kāi)發(fā)板作為數(shù)字電路設(shè)計(jì)與驗(yàn)證的重要載體,其硬件架構(gòu)設(shè)計(jì)融合了多種關(guān)鍵組件。開(kāi)發(fā)板上的FPGA芯片是實(shí)現(xiàn)邏輯功能的器件,不同型號(hào)的FPGA芯片在邏輯單元數(shù)量、存儲(chǔ)資源、接口類(lèi)型等方面存在差異。以常見(jiàn)的入門(mén)級(jí)開(kāi)發(fā)板為例,往往搭載中低端FPGA芯片,能夠滿(mǎn)足初學(xué)者對(duì)基礎(chǔ)數(shù)字電路設(shè)計(jì)的實(shí)踐需求。除了FPGA芯片,開(kāi)發(fā)板還配備電源管理模塊,該模塊通過(guò)多級(jí)電壓轉(zhuǎn)換,為FPGA芯片及其他外設(shè)提供穩(wěn)定且適配的供電電壓。例如,將外部輸入的5V電壓轉(zhuǎn)換為FPGA芯片所需的、等工作電壓。此外,復(fù)位電路的存在確保開(kāi)發(fā)板在啟動(dòng)或異常情況下能恢復(fù)到預(yù)設(shè)狀態(tài),晶振電路則為整個(gè)系統(tǒng)提供精細(xì)的時(shí)鐘信號(hào),這些硬件組件協(xié)同工作,構(gòu)成了FPGA開(kāi)發(fā)板穩(wěn)定運(yùn)行的基礎(chǔ)。 FPGA 開(kāi)發(fā)板的可重構(gòu)特性,使其能快速適應(yīng)不同項(xiàng)目需求的變化。遼寧學(xué)習(xí)FPGA開(kāi)發(fā)板套件

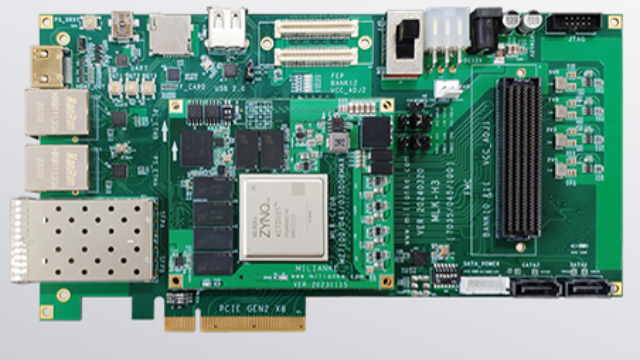

若要進(jìn)行高速數(shù)據(jù)傳輸,帶有 SFP + 光纖接口、支持高速協(xié)議的 FPGA 開(kāi)發(fā)板會(huì)是理想之選。山東開(kāi)發(fā)FPGA開(kāi)發(fā)板模塊

FPGA 開(kāi)發(fā)板的功耗管理是開(kāi)發(fā)者需要關(guān)注的重要方面。在便攜式設(shè)備或電池供電的應(yīng)用場(chǎng)景中,降低開(kāi)發(fā)板功耗尤為關(guān)鍵。開(kāi)發(fā)者可通過(guò)優(yōu)化 FPGA 邏輯設(shè)計(jì),減少不必要的邏輯翻轉(zhuǎn),降低芯片動(dòng)態(tài)功耗。合理配置開(kāi)發(fā)板外設(shè),在不使用時(shí)將其設(shè)置為低功耗模式,進(jìn)一步降低系統(tǒng)功耗。部分開(kāi)發(fā)板提供專(zhuān)門(mén)的功耗管理模塊,幫助開(kāi)發(fā)者監(jiān)控與調(diào)節(jié)功耗,通過(guò)軟件設(shè)置實(shí)現(xiàn)不同的功耗管理策略。良好的功耗管理使 FPGA 開(kāi)發(fā)板能夠在低功耗狀態(tài)下穩(wěn)定運(yùn)行,滿(mǎn)足特定應(yīng)用場(chǎng)景對(duì)功耗的嚴(yán)格要求,延長(zhǎng)設(shè)備續(xù)航時(shí)間。山東開(kāi)發(fā)FPGA開(kāi)發(fā)板模塊

- 北京FPGA開(kāi)發(fā)板教學(xué) 2025-06-25

- 浙江ZYNQFPGA開(kāi)發(fā)板核心板 2025-06-25

- 廣東安路FPGA開(kāi)發(fā)板核心板 2025-06-25

- 陜西ZYNQFPGA開(kāi)發(fā)板 2025-06-25

- 陜西XilinxFPGA開(kāi)發(fā)板套件 2025-06-25

- 江蘇ZYNQFPGA開(kāi)發(fā)板學(xué)習(xí)步驟 2025-06-25

- 江西XilinxFPGA開(kāi)發(fā)板資料下載 2025-06-25

- 浙江XilinxFPGA開(kāi)發(fā)板核心板 2025-06-25

- 天津賽靈思FPGA開(kāi)發(fā)板板卡設(shè)計(jì) 2025-06-25

- 湖北ZYNQFPGA開(kāi)發(fā)板交流 2025-06-25

- 廣東EZ-10松下光電傳感器價(jià)格合理 2025-06-25

- 2排20芯DIN41612歐式連接器 2025-06-25

- 連云港顯影機(jī)價(jià)格 2025-06-25

- 徐州微型高精度反向定位掃描儀互惠互利 2025-06-25

- 北京直流充電器價(jià)格 2025-06-25

- 云南GAINSIL聚洵電子元器件采購(gòu)商 2025-06-25

- 嘉興電視紅外線接收頭哪家好 2025-06-25

- 松江區(qū)貿(mào)易電器輔件報(bào)價(jià) 2025-06-25

- 溫州硅光硅光電二極管生產(chǎn)廠家 2025-06-25

- 杭州伺服線束訂購(gòu) 2025-06-25