-

惟精環(huán)境藻類智能分析監(jiān)測系統(tǒng),為水源安全貢獻科技力量!

-

快來擁抱無線遠程打印新時代,惟精智印云盒、讓打印變得如此簡單

-

攜手共進,惟精環(huán)境共探環(huán)保行業(yè)發(fā)展新路徑

-

惟精環(huán)境:科技賦能,守護綠水青山

-

南京市南陽商會新春聯(lián)會成功召開

-

惟精環(huán)境順利通過“江蘇省民營科技企業(yè)”復評復審

-

“自動?化監(jiān)測技術在水質(zhì)檢測中的實施與應用”在《科學家》發(fā)表

-

熱烈祝賀武漢市概念驗證中心(武漢科技大學)南京分中心掛牌成立

-

解鎖流域水質(zhì)密碼,“三維熒光水質(zhì)指紋”鎖定排污嫌疑人!

-

重磅政策,重點流域水環(huán)境綜合治理資金支持可達總投資的80%

5032差分輸出VCXO一般多少錢

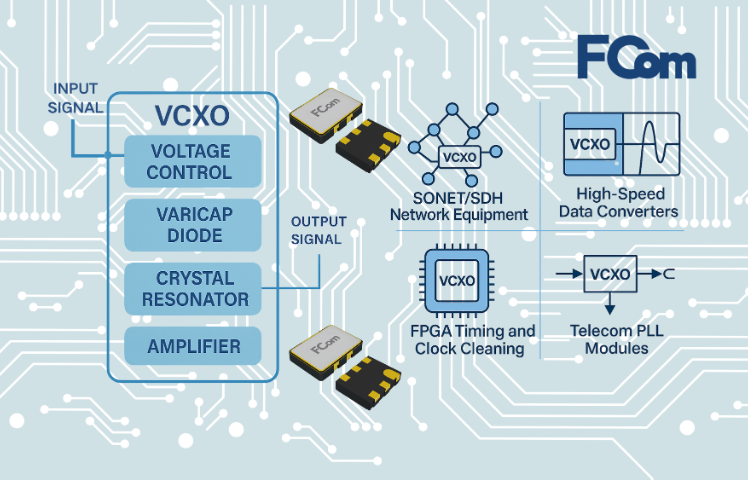

差分VCXO在多協(xié)議同步平臺中的整合優(yōu)勢 現(xiàn)代通信設備需同時支持多種協(xié)議,如以太網(wǎng)、PCIe、SATA、USB等,每個協(xié)議對參考時鐘的穩(wěn)定性和精度要求不同。差分VCXO成為多協(xié)議融合設備的理想時鐘方案。 FCom富士晶振差分輸出VCXO支持10MHz~250MHz頻率覆蓋,可為多通道PHY、MAC控制器、同步網(wǎng)絡提供統(tǒng)一時鐘基準,尤其適配Broadcom、TI、NXP等常用SoC平臺。 通過LVDS/HCSL輸出接口,系統(tǒng)可實現(xiàn)高精度多頻切換,單晶體系統(tǒng)中頻率不足或兼容性差的問題,實現(xiàn)軟硬件兼容性大化。 可編程拉頻功能(±100ppm)可與I2C/DAC控制系統(tǒng)配合,實現(xiàn)協(xié)議之間時鐘交錯、握手校正與同步誤差抵消,是跨協(xié)議通信平臺關鍵功能模塊之一。 封裝具備高可靠性與高屏蔽能力,適用于工業(yè)級、通信級與嵌入式平臺,有效抑制串擾與EMI問題,提升通信信道完整性。 FCom差分VCXO通過高性能的頻率支持與靈活調(diào)控機制,為多協(xié)議同步平臺提供統(tǒng)一、精確的時鐘支撐,是高集成系統(tǒng)不可或缺的關鍵器件。差分輸出VCXO是連接AI芯片和網(wǎng)絡接口的關鍵橋梁。5032差分輸出VCXO一般多少錢

差分輸出VCXO優(yōu)化FPGA SerDes鏈路時鐘 FPGA內(nèi)置的SerDes模塊是實現(xiàn)高速串行通信的關鍵接口,差分時鐘源是其性能表現(xiàn)的關鍵。FCom富士晶振差分輸出VCXO通過精確頻率控制與低相位抖動,為FPGA鏈路提供穩(wěn)定的參考時鐘。 在Xilinx Kintex、Intel Stratix等系列FPGA中,TX/RX PLL對時鐘源的抖動容忍度有限。FCom VCXO輸出的LVPECL或LVDS信號具備高信號完整性,幫助PLL穩(wěn)定鎖相,減少鏈路抖動傳遞。 該系列支持可編程頻率調(diào)節(jié)(如125MHz、156.25MHz、200MHz),滿足以太網(wǎng)、PCIe、Aurora等協(xié)議棧的定頻需求。頻率拉動值支持±50~150ppm調(diào)諧,便于與系統(tǒng)主控同步校準。 FCom富士晶振VCXO采用金屬密封封裝,具有良好抗熱漂性能,在高溫工況下依然保持±25ppm穩(wěn)定性,適配FPGA開發(fā)板、通信主控卡及背板互連設備。 通過將FCom的差分輸出VCXO部署于SerDes路徑,可有效抑制串擾與時鐘歪斜,提高數(shù)據(jù)眼圖開口率與誤碼性能,為高速接口提供可靠時鐘支撐。低抖動差分輸出VCXO廠家電話在多頻同步系統(tǒng)中,差分輸出VCXO是關鍵組件。

高速SSD存儲系統(tǒng)中的差分VCXO方案 NVMe SSD存儲控制器與PCIe接口依賴高質(zhì)量參考時鐘源,F(xiàn)Com富士晶振差分輸出VCXO為SSD控制系統(tǒng)提供精確的可調(diào)諧時鐘,確保數(shù)據(jù)完整性與接口兼容性。 在SSD主控芯片(如Phison E18、Marvell 88SS系列)中,VCXO用于驅(qū)動PCIe PHY或SATA PHY鏈路時鐘。FCom VCXO提供100MHz、200MHz、250MHz等常用頻率,支持HCSL/LVDS接口,滿足不同PHY輸入要求。 差分輸出可有效降低共模噪聲,提升數(shù)據(jù)通道的信號質(zhì)量,滿足Gen3/Gen4 PCIe接口在高溫高負載環(huán)境下的誤碼容忍需求。 FCom VCXO具有±50ppm調(diào)諧能力與高線性VCO響應曲線,適合與晶體時鐘清洗器或自適應PLL構建柔性頻率平臺。 使用FCom差分輸出VCXO,SSD控制系統(tǒng)能夠?qū)崿F(xiàn)穩(wěn)定的Link Training和持續(xù)高速讀寫,是企業(yè)級存儲和數(shù)據(jù)中心SSD主控理想的時鐘配套。

差分VCXO優(yōu)化邊緣服務器的時鐘架構 邊緣服務器在處理本地AI運算、IoT網(wǎng)關控制、實時圖像識別等任務時,面臨數(shù)據(jù)傳輸、存儲與計算多路徑調(diào)度問題,需好品質(zhì)時鐘支撐系統(tǒng)協(xié)調(diào)運行。 FCom差分VCXO支持包括100MHz、125MHz、200MHz等邊緣計算常用頻率,適配Intel Xeon D、NXP Layerscape、Ampere Altra等芯片平臺。 低至0.15ps的相位抖動幫助系統(tǒng)實現(xiàn)NVMe數(shù)據(jù)同步、PCIe控制器穩(wěn)定通信、DDR內(nèi)存讀取準確性等多個模塊的信號配合。 VCXO支持可編程電壓控制,可靈活適配平臺中負載變化帶來的時鐘差異,通過I2C/DAC控制完成自動調(diào)諧。 封裝采用7050高熱散設計,帶有防護金屬罩,適用于設備密集部署與高熱流區(qū)域,確保時鐘質(zhì)量長時間維持在穩(wěn)定范圍。 FCom差分VCXO幫助邊緣計算設備構建精密的定時平臺,是保證邊緣AI與分布式節(jié)點系統(tǒng)高效協(xié)同的重要基石。差分輸出VCXO優(yōu)化了FPGA中的參考時鐘鏈。

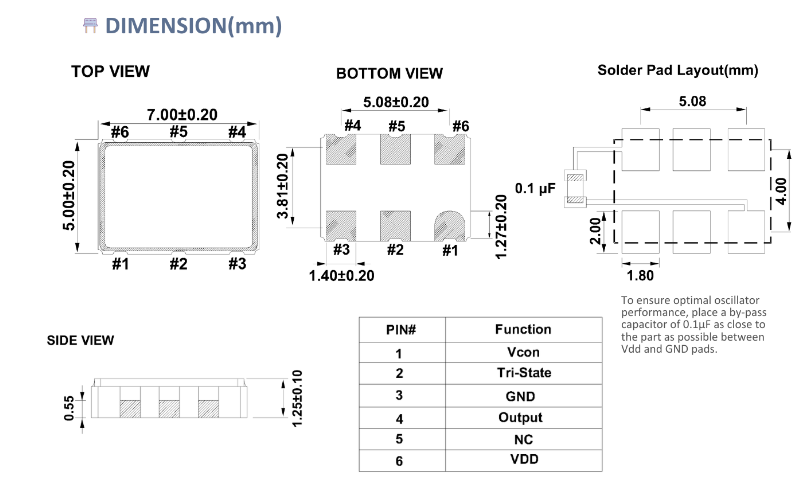

差分輸出VCXO優(yōu)化PCIe高速總線時鐘鏈路 PCI Express(PCIe)總線在高速通信系統(tǒng)中被廣應用,對參考時鐘源的抖動控制和匹配能力提出了嚴格標準。FCom富士晶振差分輸出VCXO,提供HCSL/LVDS差分輸出,專為高速總線設計。 PCIe參考時鐘要求RMS抖動小于1ps(12kHz~20MHz),F(xiàn)Com差分VCXO在該頻段內(nèi)抖動控制可達0.15ps,有效提升信號眼圖質(zhì)量,增強抗串擾能力。 FCom產(chǎn)品支持常用PCIe時鐘頻率如100MHz、125MHz、200MHz,具備可編程拉頻能力,適配Retimer或Clock Buffer架構,確保系統(tǒng)同步和Link Training穩(wěn)定。 產(chǎn)品可提供3225、5032等多種封裝,適配主板、NIC卡、加速卡等多種PCB空間需求。工作電壓支持1.8V/2.5V/3.3V,具備EMI優(yōu)化布局能力。 借助FCom富士晶振的差分輸出VCXO,PCIe鏈路能夠獲得更優(yōu)的時鐘一致性和抗干擾能力,是數(shù)據(jù)中心與高性能計算平臺中高速互連的關鍵元件。差分輸出VCXO是構建精確時鐘架構的理想選擇。新型差分輸出VCXO工廠直銷

高頻控制系統(tǒng)依賴差分輸出VCXO維持穩(wěn)定時序。5032差分輸出VCXO一般多少錢

差分VCXO在遠程測控系統(tǒng)中的信號一致性 遠程測控系統(tǒng)在深空探測、雷達、地質(zhì)遙感等領域扮演關鍵角色,對時鐘源的精度和一致性有極高要求。FCom富士晶振差分輸出VCXO為信號鏈提供同步保障。 該系列VCXO支持精密頻率點如10MHz、20MHz、40MHz及50MHz,可與頻率合成器構建窄帶測控系統(tǒng)時鐘源。 產(chǎn)品具備差分LVDS/LVPECL輸出,適用于長線纜系統(tǒng)中的數(shù)據(jù)收發(fā)模塊,提高數(shù)據(jù)一致性與抗干擾性能。 支持±50~150ppm頻率拉動,結合系統(tǒng)主控可進行閉環(huán)調(diào)頻,適配動態(tài)測控鏈路中頻漂修正。 其抗震動設計與高封裝密封等級,保障產(chǎn)品在野外、高原、艦載等嚴苛條件下長期工作。 FCom差分輸出VCXO助力遠程測控系統(tǒng)在時序驅(qū)動、數(shù)據(jù)采集和信號回讀等環(huán)節(jié)實現(xiàn)高精度控制與穩(wěn)定運行。5032差分輸出VCXO一般多少錢

- 高頻差分輸出VCXO價格查詢 2025-06-20

- 5032差分輸出VCXO一般多少錢 2025-06-20

- 多輸出差分輸出VCXO供應商 2025-06-20

- 市面主流高精度振蕩器關鍵技術解析 2025-06-19

- FCO-3C-LE低EMI振蕩器常見問題 2025-06-19

- 低相噪低抖動VCXO技術支持 2025-06-19

- 差分輸出VCXO電話 2025-06-19

- FCO-3C-HP高精度振蕩器數(shù)據(jù)手冊 2025-06-19

- 市面主流低功耗振蕩器滿足工業(yè)級寬溫需求 2025-06-19

- 工業(yè)級低功耗振蕩器性能排行榜 2025-06-19

- 全國實驗室光譜儀生產(chǎn)廠家 2025-06-20

- 本地EMW3080BP/BE行業(yè) 2025-06-20

- 佛山微型BOX箱體喇叭揚聲器價格 2025-06-20

- 北京出口IGBT模塊代理商 2025-06-20

- 多功能FPGA定制項目平臺 2025-06-20

- 湖北魚眼型DIN41612歐式連接器 2025-06-20

- 蘇州雙向二極管制造商 2025-06-20

- 青浦區(qū)哪里有智慧路燈系統(tǒng)生產(chǎn)企業(yè) 2025-06-20

- 四川AOS原廠場效應管 2025-06-20

- 江蘇不堵塞噴嘴助焊劑廠家供應 2025-06-20